#### **Introduction:**

What is a microprocessor?

It is a multifunctional Digital Circuit having both combinational and sequential components implemented in a single silicon wafer or chip. Unlike simple digital circuits designed and optimized to perform specific tasks, a microprocessor is a generalized circuit that performs a variety of tasks. The operation of the microprocessor is selected by external command called instruction. Instructions are internally decoded to generate control signals enabling hardware resources required to complete the tasks. Let us take an example to understand the multifunction of a circuit.

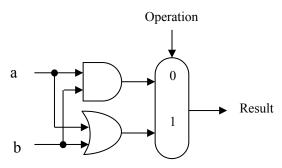

Fig.1: A circuit performing different operations on its inputs

The above is a combinational circuit that performs ANDing and ORing on its two inputs 'a' & 'b' depending upon the control input 'Operation'. For Operation = 0, Result = (a AND b) and for Operation = 1, Result = (a OR b). Further circuit blocks can be added for achieving more functions. Fig. 2 is such a circuit.

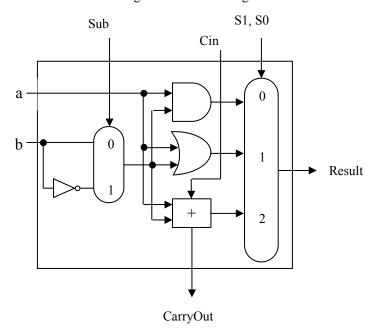

Fig.2 An one bit Arithmatic & Logic Unit

So the operations of the above circuit (can be called a simple microprocessor) can be summarized as:

| Oncontinu |     | Control | Signals |    | Oncodo           |

|-----------|-----|---------|---------|----|------------------|

| Opeartion | SUB | Cin     | S1      | S0 | Opcode           |

| AND       | 0   | X       | 0       | 0  | $0_{\mathrm{H}}$ |

| OR        | 0   | X       | 0       | 1  | 1 н              |

| ADD       | 0   | 0       | 1       | 0  | 2 н              |

| SUB       | 1   | 1       | 1       | 0  | Ен               |

Instruction Set for the machine will be:

0000 a b

0001 a b

0010 a b

1110 a b

Since the microprocessor can perform only four operations, 2 bits are enough to represent opcodes. So an instruction decoder is to be used which takes 2-bit opcode and decodes to generate control signals required for the operations.

External memory is required for storing all the instructions of a task. Also the arrangement for reading instructions sequencilaly from the memory should be there inside the microprocessor for their execution.

#### So a microprocessor is:

- It is a digital circuit implemented in a single silicon wafer or chip

- **I**t contains both combinational and sequential circuit components

- **I**t is a general purpose device

- It can implement various types of functions

- Its operation can be controlled externally

- External commands are stored in memory

- Man machine interface through I/O ports

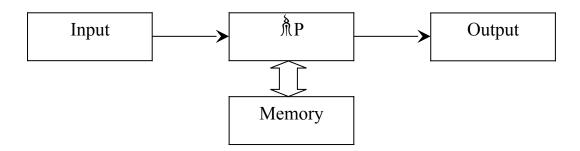

### What does a microprocessor do?

- ≤ Any electronic system, whatever complex it may be, can be built around a microprocessor

- New feature can be implemented without changing the system hardware in most of the cases.

- Typical block diagram of a  $\mathbb{R}P$  based system:

## Basic three functions done by any MP:

- Data transfer

- Arithmetic & logic operations

- Decision making

## Classification of MP:

- Based on the width of data handled by the MP for data transfer, arithmetic and logic operations by a single command or instruction.

- For example: 4-bit, 8-bit, 16-bit, 32-bit etc.

- Intel 4004 is a 4-bit microprocessor, Intel 8085 is an 8-bit MP, Intel 8088/86 is 16-bit MP etc.

- It should not be confused with the external data bus width. For example, though the external data bus width of 8088 is 8 bits, it is a 16-bit MP.

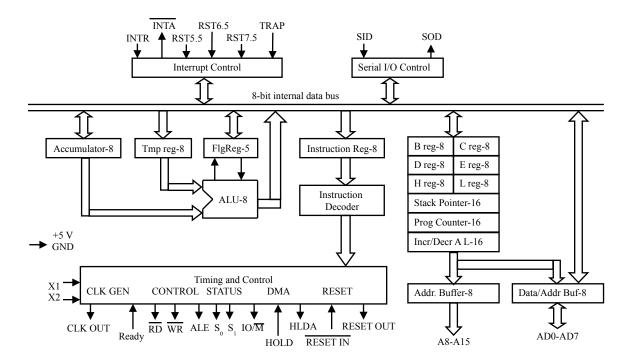

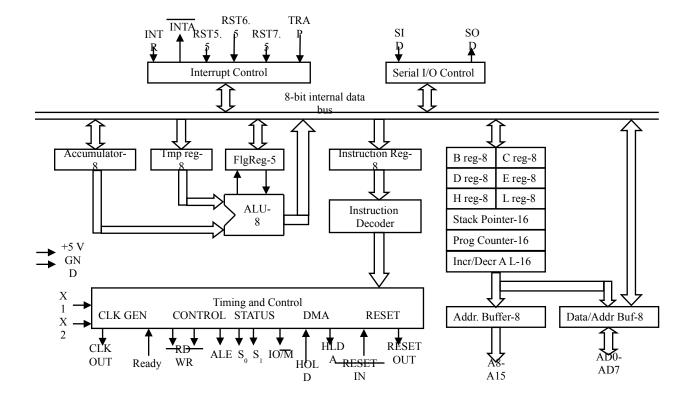

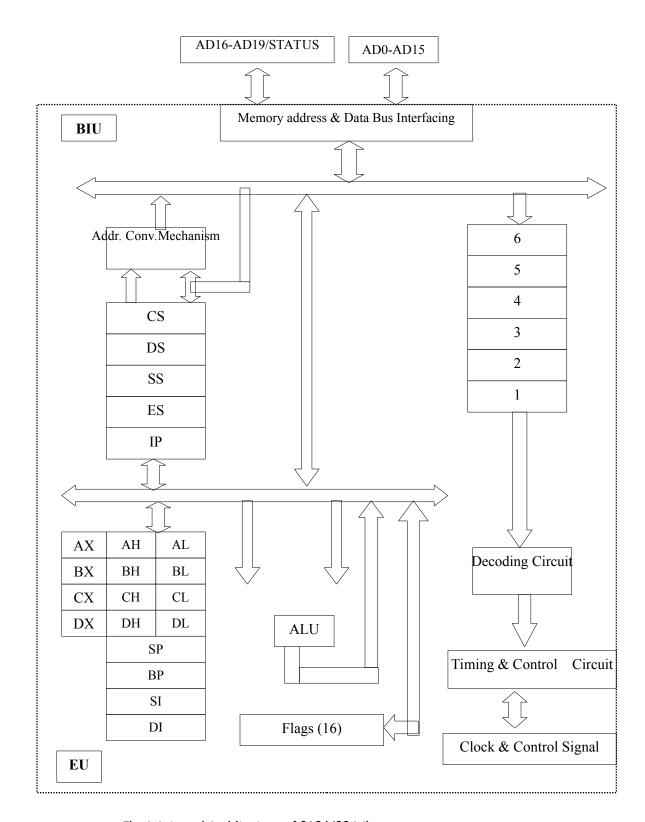

## Internal Block Diagram of 8085A:

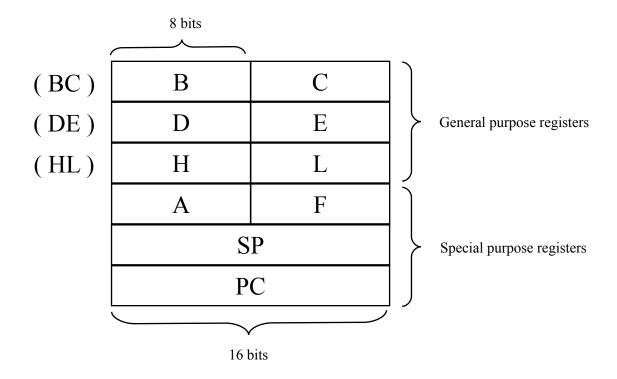

## Programming Model of 8085A:

### General Purpose Registers:

- ⇒ B, C, D, E, H, L

- They can be used in any manner by the programmer, for house keeping, memory addressing, arithmetic operation.

- Flexible to use as six 8-bit registers or as three 16-bit register pairs

- Talid register pairs are BC, DE, HL

#### Special Purpose Registers:

- A, F, SP, PC

- They are used for accumulating results from arithmetic and logic instructions and also for housekeeping.

- AF register pair is known as Program status Word (PSW) as they contain the status of the result after execution of any instruction.

### Flag Register:

- Contains 5 flag bits

- Most of the arithmetic and logic instructions modify them

- They reflect the condition of the outcome of the answer from ALU

- They are used for decision making

|   |   |   | F4 |   |   |   |    |

|---|---|---|----|---|---|---|----|

| S | Z | X | AC | X | P | X | CY |

S = 1, if -ve; Z=1, if zero; AC=1, if aux carry; P=1 for even parity (even no of 1's); CY=1, if carry/borrow

**Example:**

|                   | 1               | 0                    | 0                    |

|-------------------|-----------------|----------------------|----------------------|

|                   | 81H             | 7FH                  | 55H                  |

|                   | +7FH            | - 81H                | OR AAH               |

| Result with Carry | 1   00H         | 1   FEH              | FFH                  |

| Flags after the   | S=0, Z=1, AC=1, | S=1, Z=0, AC=0, P=0, | S=1, Z=0, AC=0, P=1, |

| operation         | P=1, CY=1       | CY=1                 | CY=0                 |

#### **Problem:**

What will be contents of the flags after executing the following operations? XRA, A; ORA, A; SUB A; CMP A

#### **Data word formats:**

- 1. Unsigned Integers:

- They are 8 bits, 16 bits or any multiple of 8 bits in width

- 8-bit unsigned integers can be found in 8-bit registers

- They can also be stored in single memory locations

- 16-bit unsigned integers are found in register pairs and in two consecutive memory locations (lower byte in low numbered memory and higher byte in high numbered memory location)

- Binary weights of 8-bit unsigned integer are:

| D7    | D6   | D5   | D4   | D3  | D2  | D1  | D0  |   |

|-------|------|------|------|-----|-----|-----|-----|---|

| (128) | (64) | (32) | (16) | (8) | (4) | (2) | (1) | 1 |

- Examples:  $1000\ 1001_2\ (89_H) = 128 + 8 + 1 = 137_{10}$

- Same logic may be extended for 16-bit or higher order integers

#### 2. Signed Integers:

- Single-byte signed integers are 7-bit numbers plus a sign bit

- Left most bit is the sign bit, 0 for +ve & 1 for -ve

- Signed 8-bit integer formats are (in 2's complement):

| Sign |                 | Sign |                             |

|------|-----------------|------|-----------------------------|

| 0    | 7-bit Magnitude | 0    | 7-bit 2's complement number |

## **Positive Integers**

## **Negative Integers**

- +ve integers range from 0 to 127

- $\stackrel{\checkmark}{=}$  -ve integers range from -1 to -128 (in 2's complement format)

- Binary weights of the bit positions for –ve numbers are:

| D7     | D6    | D5    | D4    | D3   | D2   | D1   | D0   |

|--------|-------|-------|-------|------|------|------|------|

| (-128) | (+64) | (+32) | (+16) | (+8) | (+4) | (+2) | (+1) |

- Examples:  $0111\ 1011_2\ (7B_H) = 64+32+16+8+2+1 = 123_{10}$

- $1111\ 1011_2\ (FB_H) = -128 + 32 + 16 + 8 + 2 + 1 = -5_{10}$

- Same logic may be extended for 16-bit or higher integers.

#### 3. ASCII data format:

- ≤ ASCII is the acronym for American Standard Code for Information Interchange

- **T** It is used by all manufacturer of computer peripherals

- ASCII is a 7-bit code, the 8<sup>th</sup> is used to hold the parity bit in a data communications system

- In computer systems this bit is often a logic 0.

- In some printers a 0 in the 8th bit causes it to print ASCII characters and a 1 to print graphics characters

#### 4. BCD data formats:

- BCD is the acronym for Binary Coded Decimal

- BCD is used in I/O devices for human to understand

- Expressed in two ways Packed and Unpacked BCD

- Packed BCD is stored as two digits per byte

- **≤** Examples: 79<sub>10</sub> in packed BCD is 0111 1001

- Unpacked BCD is stored as single digit per byte

- **≤** Example: 7<sub>10</sub> in unpacked BCD is 0000 0111

- Unpacked BCD codes are useful to refer look up table for code conversion etc.

- Microprocessor can also perform BCD operations but not preferred to avoid complication

#### 5. Binary Fractions:

- Binary fractions can be stored in either byte or two-byte form

- Usually they are expressed in unsigned numbers

- $\blacksquare$  Binary weights from left to right are:  $2^{-1}$ ,  $2^{-2}$ ,  $2^{-3}$ ,  $2^{-4}$ ,  $2^{-5}$  and so on

- Example:  $1010\ 0101 = 2^{-1} + 2^{-3} + 2^{-6} + 2^{-8} = 0.5 + 0.125 + 0.015625 + 0.00390625 = 0.64453125$

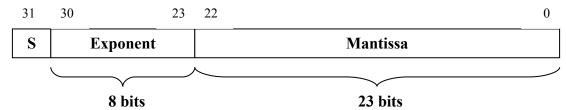

#### 6. Floating Point data:

- It is similar to scientific notation in base 10

- The floating point format is suitable to express large numbers

- It is used to store mixed as well as integer data

- Floating point numbers are often stored in four bytes

- Format of 4-byte (single precision) floating point number is:

- The left most bit indicates the sign of the mantissa

- Next 8 bits are for exponent stored in excess 127 notation

- Exponent in excess 127 is an unsigned integer that is equal to the actual exponent plus 127

- Mantissa is a normalized 23-bit number with a hidden or implied 1 in 24<sup>th</sup> bit position

- **Examples**:

$$100_{10} = 1100100_2 = 1.1001 \text{ x } 2^6$$

S Exponent Mantissa

$$-12.70_{10} = -1100.11_2 = 1.10011 \text{ x } 2^3$$

S Exponent Mantissa

## Sample Questions and answers

| Q1 | Convert the following decimal numbers to 8-bit unsigned integers: 12, 33, 55, 100, 155, 196 and 212             |

|----|-----------------------------------------------------------------------------------------------------------------|

| Q2 | Convert the following decimal numbers to 16-bit unsigned integers: 156, 222, 1000, 2009, and 10,000             |

| Q3 | Convert the following 8-bit signed integers to decimal numbers: 1111 1111, 1000 0111, 0110 1000, and 0111 0000. |

| Q4 | Convert the following decimal numbers to 8-bit signed integers: 12, -12, 32, -63, and -100                      |

| Q5 | Write the following decimal numbers as both packed and unpacked BCD numbers: 12, 3, 10, 99, 13, and 712         |

| Q6 | Convert the following decimal numbers to four-byte binary floating point form: 12, -22, 10.5, 0.002, and -4.25. |

| Q7 | Convert the following 4-byte floating point numbers into decimal numbers:                                       |

|    | 0100 0001 0100 0000 0000 0000 0000 0000                                                                         |

|    | 1011 1111 1000 0000 0000 0000 0000 0000                                                                         |

|    | 0100 1000 1110 0000 0000 0000 0000 0000                                                                         |

### Answers:

| Q1. | Decimal Number        | Corresponding 8-bit Unsigned  | Corresponding Hexadecimal      |

|-----|-----------------------|-------------------------------|--------------------------------|

|     | 40                    | Binary Number                 | Number                         |

|     | 12                    | 0000 1100                     | OC                             |

|     | 33                    | 0010 0001                     | 21                             |

|     | 55                    | 0011 0111                     | 37                             |

|     | 100                   | 0110 0100                     | 64                             |

|     | 155                   | 1001 1011                     | 9B                             |

|     | 196                   | 1100 0100                     | C4                             |

|     | 212                   | 1101 0100                     | D4                             |

| Q2. | Decimal Number        | Corresponding 16-bit Unsigned | Corresponding Hexadecimal      |

|     |                       | Binary Number                 | Number                         |

|     | 156                   | 0000 0000 1001 1100           | 009C                           |

|     | 222                   | 0000 0000 1101 1110           | 00DE                           |

|     | 1000                  | 0000 0011 1110 1000           | 03E8                           |

|     | 2009                  | 0000 0111 1101 1001           | 07D9                           |

|     | 10000                 | 0010 0111 0001 0000           | 2710                           |

| Q3. | 8-bit Signed Integers | 2's Complement if -ve         | Corresponding Decimal Number   |

|     | 1111 1111             | 0000 0001                     | -1                             |

|     | 1000 0111             | 0111 1001                     | -121                           |

|     | 0110 1000             | -                             | +104                           |

|     | 0111 0000             | -                             | +112                           |

| Q4. | Decimal Number        | -/+ & 8-bit magnitude         | 8-bit Binary in 2's Complement |

|     | 12                    | + 0000 1100                   | 0000 1100                      |

|     | -12                   | - 0000 1100                   | 1111 0100                      |

|     | 32                    | + 0010 0000                   | 0010 0000                      |

|     | -63                   | - 0011 1111                   | 1100 0001                      |

|     | -100                  | - 0110 0100                   | 1001 1100                      |

| Q5. | Decimal Number        | Packed BCD (in HEX)           | Unpacked BCD (in HEX)          |

|     | 12                    | 0001 0010 (12H)               | 0000 0010 (02H)                |

|     |                       |                               | 0000 0001 (01H)                |

|     | 3                     | 0000 0011 (03H)               | 0000 0011 (03H)                |

|     | 10                    | 0001 0000 (10H)               | 0000 0000 (00H)                |

|     |                       |                               | 0000 0001 (01H)                |

|     | 99                    | 1001 1001 (99H)               | 0000 1001 (09H)                |

\_\_\_\_\_\_

|     |                              |                               | 0000 1001 (09H)              |

|-----|------------------------------|-------------------------------|------------------------------|

|     | 13                           | 0001 0011 (13H)               | 0000 0011 (03H)              |

|     |                              |                               | 0000 0001 (01H)              |

|     | 712                          | 0000 0111 0001 0010 (0712H)   | 0000 0010 (02H)              |

|     |                              |                               | 0000 0001 (01H)              |

|     |                              |                               | 0000 0111 (07H)              |

| Q6. | Decimal Number               | Binary with fraction and sign | 4-byte floating point binary |

|     | 12                           | +1100.0                       | 0 1000 0010 1000000          |

|     | -22                          | -1 0110.0                     | 1 1000 0011 011000000        |

|     | 10.5                         | +1010.1                       | 0 1000 0010 0101000000       |

|     | 0.002                        | +0.0000 0000 1                | 0 0111 0110 0000000000       |

|     | -4.25                        | -0100.01                      | 1 1000 0001 0001000000       |

| Q7. | 4-byte floating point number | Binary with fraction and sign | Decimal number               |

|     | 0 1000 0010 100000           | +0.1 x 2 <sup>130-127</sup>   | 4                            |

|     | 1 0111 1111 000000           | -0.0 x 2 <sup>127-127</sup>   | 0                            |

|     | 0 1001 0001 110000           | +0.11 x 2 <sup>145-127</sup>  | 3x64x1024 = 196608           |

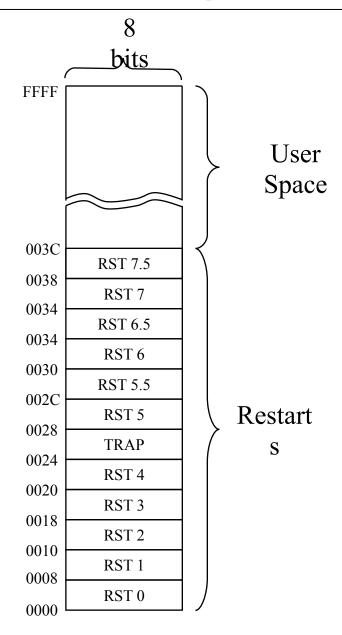

## Memory Map of 8085A:

- Tt has 16-bit address lines and 8-bit data lines.

- $\Rightarrow$  It can therefore address  $2^{16}$  or  $2^6$  x  $2^{10}$  or 64K byte memory locations.

- Memory locations are numbered from 0000H to FFFFH.

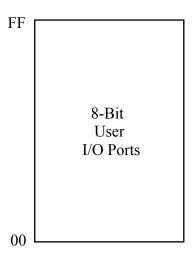

### I/O Space of 8085A:

- \* 8085A can address 256 input devices.

- Tt can also address 256 output devices.

- They are numbered from 00H to FFH.

- Tiput and Output Devices are identified by RD and WR signals respectively

- ⇒ I/O devices are accessed by IN/OUT instructions.

# **Instruction Set and Programming The 8085**

#### **Command Word Formats:**

Three different Command Word Formats are used by 8085A

One byte long Two-byte long Three-byte long 24

-----

Total - 246

Command Word (Instruction) Formats are:

| One-byte   | Op-Code |                  |                  |

|------------|---------|------------------|------------------|

| Two-byte   | Op-Code | Immediate Data   |                  |

|            | Op-Code | I/O Port Address |                  |

| Three-byte | Op-Code | Low-byte Data    | High-byte Data   |

|            | Op-Code | Low-order Addr.  | High-order Addr. |

#### **Instruction Set of 8085A:**

It can be broken into three main categories:

- 1. Data Transfer Instructions,

- 2. Arithmetic & Logic Instructions and

- 3. Program Control Instructions.

### **Rules of writing instructions:**

[Label:] op-code [des op], [source op] [; Comments]

Fields within 3<sup>rd</sup> brackets are optional.

**Addressing Modes:** The way the operands (internal/external resources like registers/meory/IO) are represented in an instruction is called addressing mode. Addressing modes may be of the following types:

- Register addressing

- Immediate addressing

- Direct addressing and

- Register indirect addressing

#### Register addressing

The instruction specifies the registers (B, C, D, E, H, L or A) or the register pairs (BC, DE, HL or SP) used with the instruction. These are all **one byte** instructions.

Examples:

MOV B, A;

ADD D etc.

### **Immediate addressing**

This mode of addressing is used when constant data are used in a program. The data are placed immediately following the op-code and stored in the program memory. 8085A has two forms immediate addressing: 8-bit and 16-bit immediate addressing. Instruction format:

byte1

byte2

byte3

| Op-code 8-bit Immediate Data |

|------------------------------|

|------------------------------|

| Op-code   Low byte of 16-bit Data   High byte of 16-bit |

|---------------------------------------------------------|

|---------------------------------------------------------|

Examples:

MVI A, 12H;

ADI 34H etc.

#### **Direct Addressing**

Instructions that directly address the memory always include the memory address of the data. This address is stored following the op-code in the program. Instruction format is:

| byte1 | byte2 | byte3 |

|-------|-------|-------|

|       |       |       |

| Op-code Low order address High order address |  |

|----------------------------------------------|--|

|----------------------------------------------|--|

Examples:

LDA 1234H;

STA 9876H etc.

## **Register Indirect Addressing:**

In some instructions register pairs BC, DE and HL are used to indicate the memory location containing the operand. This type of addressing the memory indirectly by the memory pointers is called register indirect addressing. These are all one byte instructions.

Examples:

LDAX B (or D);

STAX B (or D) etc.

## **Instruction Naming Conventions:**

The mnemonics assigned to the instructions are designed to indicate the function of the instruction. Instructions fall into the following functional categories:

| SL   | Mnemonic      | Purpose                                                                                       | Syntax          | Note                                                                                      |

|------|---------------|-----------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------|

| Data | Transfer Ins  |                                                                                               |                 |                                                                                           |

| The  | data transfer | instructions move data between reg                                                            | gisters or betw | een memory and register.                                                                  |

| 1    | MVI           | Move Immediate data                                                                           | MVI rd, d8      | rd may be one of 7 8-bit registers and M. M is the memory pointed to by HL register pair. |

| 2    | MOV           | Move data between 8-bit register to register and between register to memory pointed to by HL. | MOV rd, rs      | rd and rs may be any combination of 7 8-bit registers and M except M, M.                  |

| 3    | LDA           | Load Accumulator Directly from Memory                                                         | LDA a16         | A = [a16], a16 is 16-bit address of a memory location                                     |

| 4    | STA           | Store Accumulator Directly in Memory                                                          | STA a16         | [a16] = A                                                                                 |

| 5    | LHLD          | Load H & L Registers Directly from Memory                                                     | LHLD a16        | L = [a16], H = [a16+1]                                                                    |

| 6    | SHLD          | Store H & L Registers Directly in Memory                                                      | SHLD a16        | [a16] = L, [a16+1] = H                                                                    |

| 7    | LXI           | Load Register Pair with 16-bit Immediate data                                                 | LXI rp          | rp may be one of HL, BC, DE, SP.                                                          |

| 8    | LDAX          | Load Accumulator from Address in Register Pair                                                | LDAX rp         | rp may be one of BC and DE                                                                |

| 9    | STAX          | Store Accumulator in Address in Register Pair                                                 | STAX rp         | rp may be one of BC and DE                                                                |

| 10   | XCHG          | Exchange H & L with D & E                                                                     | XCHG            |                                                                                           |

| 11   | XTHL          | Exchange Top of Stack with H & L                                                              | XTHL            |                                                                                           |

|      | hmetic Group  |                                                                                               |                 |                                                                                           |

|      |               | ructions are used to perform arithmetic                                                       | _ •             |                                                                                           |

| 12   | ADI           | Add Immediate Data to Accumulator                                                             | ADI d8          | d8 is the 8-bit immediate data                                                            |

| 13   | ADD           | Add to Accumulator                                                                            | ADD r           | r may be one of 7 8-bit registers and M                                                   |

| 14   | ADC           | Add to Accumulator Using Carry Flag                                                           | ADC r           | r may be one of 7 8-bit registers and M                                                   |

| 15   | ACI           | Add Immediate data to Accumulator Using Carry                                                 | ACI r           | r may be one of 7 8-bit registers and M                                                   |

| 16   | SUI           | Subtract Immediate Data from Accumulator                                                      | SUI d8          | d8 is the 8-bit immediate data                                                            |

| 17   | SUB           | Subtract from Accumulator                                                                     | SUB r           | r may be one of 7 8-bit registers and M                                                   |

| 18   | SBI           | Subtract Immediate from                                                                       | SBI d8          | d8 is the 8-bit immediate data                                                            |

|    |     | Accumulator Using Borrow (Carry) Flag                                          |        |                                         |

|----|-----|--------------------------------------------------------------------------------|--------|-----------------------------------------|

| 19 | SBB | Subtract from Accumulator Using Borrow (Carry) Flag                            | SBB r  | r may be one of 7 8-bit registers and M |

| 20 | INR | Increment Specified Byte by<br>One                                             | INR r  | r may be one of 7 8-bit registers and M |

| 21 | DCR | Decrement Specified Byte by<br>One                                             | DCR r  | r may be one of 7 8-bit registers and M |

| 22 | INX | Increment Register Pair by One                                                 | INX rp | rp may be one of BC, DE, HL, SP         |

| 23 | DCX | Decrement Register Pair by<br>One                                              | DCX rp | rp may be one of BC, DE, HL, SP         |

| 24 | DAD | Double Register Add; Add<br>Content of Register Pair to H<br>& L Register Pair | DAD rp | rp may be one of BC, DE, HL, SP         |

| 25 | DAA | Decimal adjust accumulator after BCD addition                                  | DAA    |                                         |

## **Logical Group**

This group performs logical (Boolean) operations on data in registers and memory and on condition flags.

The logical AND, OR, and Exclusive OR instructions enable you to set specific bits in the accumulator ON or OFF.

| 26 | ANI | Logical AND with Accumulator                     | ANI d8 | d8 is the 8-bit immediate data          |

|----|-----|--------------------------------------------------|--------|-----------------------------------------|

|    |     | Using Immediate Data                             |        |                                         |

| 27 | ANA | Logical AND with Accumulator                     | ANA r  | r may be one of 7 8-bit registers and M |

| 28 | ORA | Logical OR with Accumulator                      | ORA r  | r may be one of 7 8-bit registers and M |

| 29 | ORI | Logical OR with Accumulator Using Immediate Data | ORI d8 | d8 is the 8-bit immediate data          |

| 30 | XRI | Exclusive OR Using Immediate Data                | SRI d8 | d8 is the 8-bit immediate data          |

| 31 | XRA | Exclusive Logical OR with Accumulator            | XRA r  | r may be one of 7 8-bit registers and M |

| 32 | CPI | Compare Using Immediate Data                     | CPI d8 | d8 is the 8-bit immediate data          |

| 33 | CMP | Compare                                          | CMP r  | r may be one of 7 8-bit registers and M |

| 34 | RLC | Rotate Accumulator Left                          | RLC    | Rotation by one bit position            |

| 35 | RRC | Rotate Accumulator Right                         | RRC    | Rotation by one bit position            |

| 36 | RAL | Rotate Left Through Carry                        | RAL    | Rotation by one bit position            |

| 37 | RAR | Rotate Right Through Carry                       | RAR    | Rotation by one bit position            |

| 38 | CMA | Complement Accumulator                           | CMA    |                                         |

| 39 | CMC | Complement Carry Flag                            | CMC    |                                         |

| 40 | STC | Set Carry Flag                                   | STC    |                                         |

|    |     |                                                  |        |                                         |

## **Branch Group:**

The branching instructions alter normal sequence of program flow, either unconditionally or conditionally. The unconditional branching instructions are as follows:

```

JMP Jump

CALL Call

RET Return

```

Conditional branching instructions examine the status of one of four condition flags to determine whether the specified branch is to be executed. The conditions that may be specified are as follows:

```

NZ

Not Zero (Z = 0)

Z

Zero (Z = 1)

NC

No Carry (C = 0)

Carry (C = 1)

C

Parity Odd (P = 0)

PO

Parity Even (P = 1)

PE

P

Plus (S = 0)

Minus (S = 1)

M

```

Thus, the conditional branching instructions are specified as follows:

| Jumps | s Calls | Returns |               |

|-------|---------|---------|---------------|

| JC    | CC      | RC      | (Carry)       |

| JNC   | CNC     | RNC     | (No Carry)    |

| JZ    | CZ      | RZ      | (Zero)        |

| JNZ   | CNZ     | RNZ     | (Not Zero)    |

| JP    | CP      | RP      | (Plus)        |

| JM    | CM      | RM      | (Minus)       |

| JPE   | CPE     | RPE     | (Parity Even) |

| JPO   | CPO     | RPO     | (Parity Odd)  |

Two other instructions can affect a branch by replacing the contents or the program counter:

```

PCHL Move H & L to Program Counter

RST Special Restart Instruction Used with Interrupts

```

## Stack, I/O and Machine Control Instructions:

The following instructions affect the Stack and/or Stack Pointer:

```

PUSH Push Two bytes of Data onto the Stack

POP Pop Two Bytes of Data off the Stack

XTHL Exchange Top of Stack with H & L

SPHL Move content of H & L to Stack Pointer

```

#### The I/O instructions are as follows:

IN Initiate Input OperationOUT Initiate Output Operation

## The Machine Control instructions are as follows:

EI Enable Interrupt System

DI Disable Interrupt System

HLT Halt

NOP No Operation

### **8085A Instruction Set:**

| SL    | Manamania        | On anda         | Deuton | Clask | Eumotion     |   |   | Flag | 3 |   |

|-------|------------------|-----------------|--------|-------|--------------|---|---|------|---|---|

| SL    | Mnemonic         | Op-code         | Bytes  | Clock | Function     | Z | C | A    | S | P |

| Imm   | ediate data tran | sfer instructio |        |       |              |   |   |      |   |   |

| 1     | MVI B, d8        | 06-d8           | 2      | 7     | B = d8       | - | - | -    | - | - |

| 2     | MVI C, d8        | 0E-d8           | 2      | 7     | C = d8       | - | - | -    | - | - |

| 3     | MVI D, d8        | 16-d8           | 2      | 7     | D = d8       | - | - | -    | - | - |

| 4     | MVI E, d8        | 1E-d8           | 2      | 7     | E = d8       | - | - | -    | - | - |

| 5     | MVI H, d8        | 26-d8           | 2      | 7     | H = d8       | - | - | -    | - | - |

| 6     | MVI L, d8        | 2E-d8           | 2      | 7     | L = d8       | - | - | -    | - | - |

| 7     | MVI M, d8        | 36-d8           | 2      | 10    | M = d8       | - | - | -    | - | - |

| 8     | MVI A, d8        | 3E-d8           | 2      | 7     | A = d8       | - | - | -    | - | - |

| 9     | LXI B, d16       | 01-ll-hh        | 3      | 10    | BC = d16     | - | - | -    | - | - |

| 10    | LXI D, d16       | 11-ll-hh        | 3      | 10    | DE = d16     | - | - | -    | - | - |

| 11    | LXI H, d16       | 21-ll-hh        | 3      | 10    | HL = d16     | - | - | -    | - | - |

| 12    | LXI SP, d16      | 31-ll-hh        | 3      | 10    | SP = d16     | - | - | -    | - | - |

| Direc | ct Data Transfei | •               |        |       |              |   |   |      |   |   |

| 13    | LDA a16          | 3A-ll-hh        | 3      | 13    | A = [a16]    | - | - | -    | - | - |

| 14    | STA a16          | 32-ll-hh        | 3      | 13    | [a16] = A    | - | - | -    | - | - |

| 15    | LHLD a16         | 2A-ll-hh        | 3      | 16    | HL = [a16]   | - | - | -    | - | - |

| 16    | SHLD a16         | 22-ll-hh        | 3      | 16    | [a16] = HL   | - | - | -    | - | - |

| Indir | ect Data Transf  | er Instruction  | ıs     |       |              |   |   |      |   |   |

| 17    | LDAX B           | 0A              | 1      | 7     | A = [BC]     | - | - | -    | - | - |

| 18    | LDAX D           | 1A              | 1      | 7     | A = [DE]     | - | - | -    | - | - |

| 19    | STAX B           | 02              | 1      | 7     | [BC] = A     | - | - | -    | - | - |

| 20    | STAX D           | 12              | 1      | 7     | [DE] = A     | - | - | -    | - | - |

| Regis | ster Data Trans  | fer Instruction | ns     |       |              |   |   |      |   |   |

| 21    | MOV B, B         | 40              | 1      | 4     | B = B        | - | - | -    | - | - |

| 22    | MOV B, C         | 41              | 1      | 4     | B = C        | - | - | -    | - | - |

| 23    | MOV B, D         | 42              | 1      | 4     | B = D        | - | - | -    | - | - |

| 24    | MOV B, E         | 43              | 1      | 4     | B = E        | - | - | -    | - | - |

| 25    | MOV B, H         | 44              | 1      | 4     | B = H        | - | - | -    | - | - |

| 26    | MOV B, L         | 45              | 1      | 4     | $B = \Gamma$ | - | - | -    | - | - |

| 27    | MOV B, M         | 46              | 1      | 7     | B = M        | - | - | -    | - | - |

\_\_\_\_\_\_

| CI | M        | 0 1-    | D4    | Clock | E4'          |   | Flag |   |   |   |  |  |

|----|----------|---------|-------|-------|--------------|---|------|---|---|---|--|--|

| SL | Mnemonic | Op-code | Bytes | Clock | Function     | Z | C    | A | S | P |  |  |

| 28 | MOV B, A | 47      | 1     | 4     | B = A        | - | -    | - | - | - |  |  |

| 29 | MOV C, B | 48      | 1     | 4     | C = B        | - | -    | - | - | - |  |  |

| 30 | MOV C, C | 49      | 1     | 4     | C = C        | - | -    | - | - | - |  |  |

| 31 | MOV C, D | 4A      | 1     | 4     | C = D        | - | -    | - | - | - |  |  |

| 32 | MOV C, E | 4B      | 1     | 4     | C = E        | - | -    | - | - | - |  |  |

| 33 | MOV C, H | 4C      | 1     | 4     | C = H        | - | -    | - | - | - |  |  |

| 34 | MOV C, L | 4D      | 1     | 4     | $C = \Gamma$ | - | -    | - | - | - |  |  |

| 35 | MOV C, M | 4E      | 1     | 7     | C = M        | - | -    | - | - | - |  |  |

| 36 | MOV C, A | 4F      | 1     | 4     | C = A        | - | -    | - | - | - |  |  |

| 37 | MOV D, B | 50      | 1     | 4     | D = B        | - | -    | - | - | - |  |  |

| 38 | MOV D, C | 51      | 1     | 4     | D = C        | - | -    | - | - | - |  |  |

| 39 | MOV D, D | 52      | 1     | 4     | D = D        | - | -    | - | - | - |  |  |

| 40 | MOV D, E | 53      | 1     | 4     | D = E        | - | -    | - | - | - |  |  |

| 41 | MOV D, H | 54      | 1     | 4     | D = H        | - | -    | - | - | - |  |  |

| 42 | MOV D, L | 55      | 1     | 4     | $D = \Gamma$ | - | -    | - | - | - |  |  |

| 43 | MOV D, M | 56      | 1     | 7     | D = M        | - | -    | - | - | - |  |  |

| 44 | MOV D, A | 57      | 1     | 4     | D = A        | - | -    | - | - | - |  |  |

| 45 | MOV E, B | 58      | 1     | 4     | E = B        | - | -    | - | - | - |  |  |

| 46 | MOV E, C | 59      | 1     | 4     | E = C        | - | -    | - | - | - |  |  |

| 47 | MOV E, D | 5A      | 1     | 4     | E = D        | - | -    | - | - | - |  |  |

| 48 | MOV E, E | 5B      | 1     | 4     | E = E        | - | -    | - | - | - |  |  |

| 49 | MOV E, H | 5C      | 1     | 4     | E = H        | - | -    | - | - | - |  |  |

| 50 | MOV E, L | 5D      | 1     | 4     | $E = \Gamma$ | - | -    | - | - | - |  |  |

| 51 | MOV E, M | 5E      | 1     | 7     | E = M        | - | -    | - | - | - |  |  |

| 52 | MOV E, A | 5F      | 1     | 4     | E = A        | - | -    | - | - | - |  |  |

| 53 | MOV H, B | 60      | 1     | 4     | H = B        | - | -    | - | - | - |  |  |

| 54 | MOV H, C | 61      | 1     | 4     | H = C        | - | -    | - | - | - |  |  |

| 55 | MOV H, D | 62      | 1     | 4     | H = D        | - | -    | - | - | - |  |  |

| 56 | MOV H, E | 63      | 1     | 4     | H = E        | - | -    | - | - | - |  |  |

| 57 | MOV H, H | 64      | 1     | 4     | H = H        | - | -    | - | - | - |  |  |

| 58 | MOV H, L | 65      | 1     | 4     | H = L        | - | -    | - | - | - |  |  |

| 59 | MOV H, M | 66      | 1     | 7     | H = M        | - | -    | - | - | - |  |  |

| 60 | MOV H, A | 67      | 1     | 4     | H = A        | - | -    | - | - | - |  |  |

| 61 | MOV L, B | 68      | 1     | 4     | L = B        | - | -    | - | - | - |  |  |

| 62 | MOV L, C | 69      | 1     | 4     | L = C        | - | -    | - | - | - |  |  |

| 63 | MOV L, D | 6A      | 1     | 4     | L = D        | - | -    | - | - | - |  |  |

| 64 | MOV L, E | 6B      | 1     | 4     | $\Gamma = E$ | - | -    | - | - | - |  |  |

| 65 | MOV L, H | 6C      | 1     | 4     | L = H        | - | -    | - | - | - |  |  |

| 66 | MOV L, L | 6D      | 1     | 4     | L = L        | - | -    | - | - | - |  |  |

| 67 | MOV L, M | 6E      | 1     | 7     | L = M        | - | -    | - | - | - |  |  |

| 68 | MOV L, A | 6F      | 1     | 4     | L = A        | - | -    | - | - | - |  |  |

| 69 | MOV M, B | 70      | 1     | 7     | M = B        | - | -    | - | - | - |  |  |

| 70 | MOV M, C | 71      | 1     | 7     | M = C        | - | -    | - | - | - |  |  |

| 71 | MOV M, D | 72      | 1     | 7     | M = D        | - | -    | - | - | - |  |  |

| 72 | MOV M, E | 73      | 1     | 7     | M = E        | - | -    | - | - | - |  |  |

| 73 | MOV M, H | 74      | 1     | 7     | M = H        | - | -    | - | - | - |  |  |

| 74 | MOV M, L | 75      | 1     | 7     | M = L        | - | -    | - | - | - |  |  |

| SL    | Mnemonic        | Op-code | Bytes    | Clock | Function               | Flag |   |   |   |          |  |

|-------|-----------------|---------|----------|-------|------------------------|------|---|---|---|----------|--|

| SL    |                 | Ор-соис | Dytes    | CIOCK | Function               | Z    | C | A | S | P        |  |

| -     | MOV M, M        | -       |          | -     |                        |      |   |   |   |          |  |

| 75    | MOV M, A        | 77      | 1        | 7     | M = A                  | -    | - | - | - | <u>-</u> |  |

| 76    | MOV A, B        | 78      | 1        | 4     | A = B                  | -    | - | - | - | -        |  |

| 77    | MOV A, C        | 79      | 1        | 4     | A = C                  | -    | - | - | - | -        |  |

| 78    | MOV A, D        | 7A      | 1        | 4     | A = D                  | -    | - | - | - | -        |  |

| 79    | MOV A, E        | 7B      | 1        | 4     | A = E                  | -    | - | - | - | -        |  |

| 80    | MOV A, H        | 7C      | 1        | 4     | A = H                  | -    | - | - | - | <u> </u> |  |

| 81    | MOV A, L        | 7D      | 1        | 4     | A = L                  | -    | - | - | - | -        |  |

| 82    | MOV A, M        | 7E      | 1        | 7     | A = M                  | -    | - | - | - | -        |  |

| 83    | MOV A, A        | 7F      | 1        | 4     | A = A                  | -    | - | - | - |          |  |

|       | Data Transfer   |         |          | 1     | 1                      |      | ı |   |   |          |  |

| 84    | POP B           | C1      | 1        | 10    | C = [SP], B = [SP+1]   | -    | - | - | - | -        |  |

| 85    | POP D           | D1      | 1        | 10    | E = [SP], D = [SP+1]   |      | - | - | - | -        |  |

| 86    | POP H           | E1      | 1        | 10    | L = [SP], H = [SP+1]   | -    | - | - | - | -        |  |

| 87    | POP PSW         | F1      | 1        | 10    | A = [SP], F = [SP+1]   | *    | * | * | * | *        |  |

| 88    | PUSH B          | C5      | 1        | 10    | [SP-1] = B, [SP-2] = C | -    | - | - | - | -        |  |

| 89    | PUSH D          | D5      | 1        | 10    | [SP-1] = D, [SP-2] = E | -    | - | - | - | -        |  |

| 90    | PUSH H          | E5      | 1        | 10    | [SP-1] = H, [SP-2] = L | -    | - | - | - | -        |  |

| 91    | PUSH PSW        | F5      | 1        | 10    | [SP-1] = F, [SP-2] = A | -    | - | - | - | -        |  |

| 92    | XTHL            | E3      | 1        | 16    | HL ↔ stack data        | -    | - | - | - | -        |  |

|       | ellaneous Data  |         | ructions |       |                        |      |   |   |   |          |  |

| 93    | IN p8           | DB-p8   | 2        | 10    | Inputs data to A       | -    | - | - | - | -        |  |

| 94    | OUT p8          | D3-p8   | 2        | 10    | Outputs data from A    | -    | - | - | - | <u> </u> |  |

| 95    | SPHL            | F9      | 1        | 6     | SP = HL                | -    | - | - | - | -        |  |

| 96    | XCHG            | EB      | 1        | 4     | HL ↔ DE                | -    | - | - | - | -        |  |

|       | metic and Logi  |         | S        |       |                        |      |   |   |   |          |  |

|       | Binary Additio  |         | 1        | 1     |                        |      |   |   |   | ,        |  |

| 97    | ADI d8          | C6-d8   | 2        | 7     | A = A + d8             | *    | * | * | * | *        |  |

| 98    | ADD B           | 80      | 1        | 4     | A = A + B              | *    | * | * | * | *        |  |

| 99    | ADD C           | 81      | 1        | 4     | A = A + C              | *    | * | * | * | *        |  |

| 100   | ADD D           | 82      | 1        | 4     | A = A + D              | *    | * | * | * | *        |  |

| 101   | ADD E           | 83      | 1        | 4     | A = A + E              | *    | * | * | * | *        |  |

| 102   | ADD H           | 84      | 1        | 4     | A = A + H              | *    | * | * | * | *        |  |

| 103   | ADD L           | 85      | 1        | 4     | A = A + L              | *    | * | * | * | *        |  |

| 104   | ADD M           | 86      | 1        | 7     | A = A + M              | *    | * | * | * | *        |  |

| 105   | ADD A           | 87      | 1        | 4     | A = A + A              | *    | * | * | * | *        |  |

|       | tion with Carry |         |          |       |                        |      |   |   |   |          |  |

| 106   | ACI d8          | CE-d8   | 2        | 7     | A = A + d8 + CY        | *    | * | * | * | *        |  |

| 107   | ADC B           | 88      | 1        | 4     | A = A + B + CY         | *    | * | * | * | *        |  |

| 108   | ADC C           | 89      | 1        | 4     | A = A + C + CY         | *    | * | * | * | *        |  |

| 109   | ADC D           | 8A      | 1        | 4     | A = A + D + CY         | *    | * | * | * | *        |  |

| 110   | ADC E           | 8B      | 1        | 4     | A = A + E + CY         | *    | * | * | * | *        |  |

| 111   | ADC H           | 8C      | 1        | 4     | A = A + H + CY         | *    | * | * | * | *        |  |

| 112   | ADC L           | 8D      | 1        | 4     | A = A + L + CY         | *    | * | * | * | *        |  |

| 113   | ADC M           | 8E      | 1        | 7     | A = A + M + CY         | *    | * | * | * | *        |  |

| 114   | ADC A           | 8F      | 1        | 4     | A = A + A + CY         | *    | * | * | * | *        |  |

| 16-bi | t Addition      |         |          |       |                        |      |   |   |   |          |  |

\_\_\_\_\_\_

| CI    | Mnomonio       | onia On anda | Drytos | Clock | Eumation                                      |          |   | Flag | 3 |   |

|-------|----------------|--------------|--------|-------|-----------------------------------------------|----------|---|------|---|---|

| SL    | Mnemonic       | Op-code      | Bytes  | Clock | Function                                      | Z        | C | A    | S | P |

| 115   | DAD B          | 09           | 1      | 10    | HL = HL + BC                                  | -        | * | -    | - | - |

| 116   | DAD D          | 19           | 1      | 10    | HL = HL + DE                                  | -        | * | -    | - | - |

| 117   | DAD H          | 29           | 1      | 10    | HL = HL + HL                                  | -        | * | -    | - | - |

| 118   | DAD SP         | 39           | 1      | 10    | HL = HL + SP                                  | -        | * | -    | - | - |

| BCD   | Addition       |              | _      |       |                                               |          |   |      |   |   |

| 119   | DAA            | 27           | 1      | 4     | Decimal adjust accumulator after BCD addition | *        | * | *    | * | * |

| Incre | ment           |              |        | ļ     | WW3171511                                     |          |   |      |   |   |

| 120   | INR B          | 04           | 1      | 4     | B = B + 1                                     | *        | _ | *    | * | * |

| 121   | INR C          | 0C           | 1      | 4     | C = C + 1                                     | *        | _ | *    | * | * |

| 122   | INR D          | 14           | 1      | 4     | D = D + 1                                     | *        | _ | *    | * | * |

| 123   | INR E          | 1C           | 1      | 4     | E = E + 1                                     | *        | - | *    | * | * |

| 124   | INR H          | 24           | 1      | 4     | H = H + 1                                     | *        | - | *    | * | * |

| 125   | INR L          | 2C           | 1      | 4     | L = L + 1                                     | *        | - | *    | * | * |

| 126   | INR M          | 34           | 1      | 10    | M = M + 1                                     | *        | - | *    | * | * |

| 127   | INR A          | 3C           | 1      | 4     | A = A + 1                                     | *        | _ | *    | * | * |

| 128   | INX B          | 03           | 1      | 6     | BC = BC + 1                                   | <b>-</b> | _ | -    | _ | - |

| 129   | INX D          | 13           | 1      | 6     | DE = DE + 1                                   | T-       | _ | -    | _ | - |

| 130   | INX H          | 23           | 1      | 6     | HL = HL + 1                                   | -        | - | -    | - | - |

| 131   | INX SP         | 33           | 1      | 6     | SP = SP + 1                                   | <b>-</b> | _ | -    | - | - |

|       | action         |              |        |       |                                               |          |   |      |   |   |

|       | Subtraction    |              |        |       |                                               |          |   |      |   |   |

| 132   | SUI d8         | D6-d8        | 1      | 7     | A = A - d8                                    | *        | * | *    | * | * |

| 133   | SUB B          | 90           | 1      | 4     | A = A - B                                     | *        | * | *    | * | * |

| 134   | SUB C          | 91           | 1      | 4     | A = A - C                                     | *        | * | *    | * | * |

| 135   | SUB D          | 92           | 1      | 4     | A = A - D                                     | *        | * | *    | * | * |

| 136   | SUB E          | 93           | 1      | 4     | A = A - E                                     | *        | * | *    | * | * |

| 137   | SUB H          | 94           | 1      | 4     | A = A - H                                     | *        | * | *    | * | * |

| 138   | SUB L          | 95           | 1      | 4     | A = A - L                                     | *        | * | *    | * | * |

| 139   | SUB M          | 96           | 1      | 7     | A = A - M                                     | *        | * | *    | * | * |

| 140   | SUB A          | 97           | 1      | 4     | A = A - A                                     | 1        | 0 | 0    | 0 | 1 |

|       | act with Borro |              | -      | •     |                                               |          |   |      |   |   |

| 141   | SBI d8         | DE-d8        | 2      | 7     | A = A - d8 - CY                               | *        | * | *    | * | * |

| 142   | SBB B          | 98           | 1      | 4     | A = A - B - CY                                | *        | * | *    | * | * |

| 143   | SBB C          | 99           | 1      | 4     | A = A - C - CY                                | *        | * | *    | * | * |

| 144   | SBB D          | 9A           | 1      | 4     | A = A - D - CY                                | *        | * | *    | * | * |

| 145   | SBB E          | 9B           | 1      | 4     | A = A - E - CY                                | *        | * | *    | * | * |

| 146   | SBB H          | 9C           | 1      | 4     | A = A - H - CY                                | *        | * | *    | * | * |

| 147   | SBB L          | 9D           | 1      | 4     | A = A - L - CY                                | *        | * | *    | * | * |

| 148   | SBB M          | 9E           | 1      | 7     | A = A - M - CY                                | *        | * | *    | * | * |

| 149   | SBB A          | 9F           | 1      | 4     | A = A - A - CY                                | *        | * | *    | * | * |

|       | ement          | 1            |        | 1     | 1                                             |          |   |      |   | - |

| 150   | DCR B          | 05           | 1      | 4     | B = B - 1                                     | *        | - | *    | * | * |

| 151   | DCR C          | 0D           | 1      | 4     | C = C - 1                                     | *        | - | *    | * | * |

| 152   | DCR D          | 15           | 1      | 4     | D = D - 1                                     | *        | - | *    | * | * |

| 153   | DCR E          | 1D           | 1      | 4     | E = E - 1                                     | *        | - | *    | * | * |

\_\_\_\_\_\_

| SL    | Mnemonic       | On anda | Dystos | Clock | E               | Flag |   |   |   |   |  |  |

|-------|----------------|---------|--------|-------|-----------------|------|---|---|---|---|--|--|

| SL    | Minemonic      | Op-code | Bytes  | Clock | Function        | Z    | C | A | S | P |  |  |

| 154   | DCR H          | 25      | 1      | 4     | H = H - 1       | *    | - | * | * | * |  |  |

| 155   | DCR L          | 2D      | 1      | 4     | L = L - 1       | *    | - | * | * | * |  |  |

| 156   | DCR M          | 35      | 1      | 10    | M = M - 1       | *    | - | * | * | * |  |  |

| 157   | DCR A          | 3D      | 1      | 4     | A = A - 1       | *    | - | * | * | * |  |  |

| 158   | DCX B          | 0B      | 1      | 6     | BC = BC - 1     | -    | - | - | - | - |  |  |

| 159   | DCX D          | 1B      | 1      | 6     | DE = DE - 1     | -    | - | - | - | - |  |  |

| 160   | DCX H          | 2B      | 1      | 6     | HL = HL - 1     | -    | - | - | - | - |  |  |

| 161   | DCX SP         | 33      | 1      | 6     | SP = SP - 1     | -    | - | - | - | - |  |  |

| Com   |                |         |        |       | 1               |      |   |   |   |   |  |  |

| 162   | CPI d8         | FE-d8   | 2      | 7     | Flags = A - d8  | *    | * | * | * | * |  |  |

| 163   | CMP B          | B8      | 1      | 4     | Flags = A - B   | *    | * | * | * | * |  |  |

| 164   | CMP C          | B9      | 1      | 4     | Flags = A - C   | *    | * | * | * | * |  |  |

| 165   | CMP D          | BA      | 1      | 4     | Flags = A - D   | *    | * | * | * | * |  |  |

| 166   | CMP E          | BB      | 1      | 4     | Flags = A - E   | *    | * | * | * | * |  |  |

| 167   | CMP H          | BC      | 1      | 4     | Flags = A - H   | *    | * | * | * | * |  |  |

| 168   | CMP L          | BD      | 1      | 4     | Flags = A - L   | *    | * | * | * | * |  |  |

| 169   | CMP M          | BE      | 1      | 7     | Flags = A - M   | *    | * | * | * | * |  |  |

| 170   | CMP A          | BF      | 1      | 4     | Flags = A - A   | 1    | 0 | 0 | 0 | 1 |  |  |

| Logic | Instructions   |         | ·      |       |                 |      |   |   |   |   |  |  |

| Inver | sion           |         |        |       |                 |      |   |   |   |   |  |  |

| 171   | CMA            | 2F      | 1      | 4     | $A = \bar{A}$   | -    | - | - | - | - |  |  |

| The A | AND Operation  | n       | •      | •     |                 | •    |   |   |   |   |  |  |

| 172   | ANI d8         | E6-d8   | 2      | 7     | A = A * d8      | *    | 0 | 0 | * | * |  |  |

| 173   | ANA B          | A0      | 1      | 4     | A = A * B       | *    | 0 | * | * | * |  |  |

| 174   | ANA C          | A1      | 1      | 4     | A = A * C       | *    | 0 | * | * | * |  |  |

| 175   | ANA D          | A2      | 1      | 4     | A = A * D       | *    | 0 | * | * | * |  |  |

| 176   | ANA E          | A3      | 1      | 4     | A = A * E       | *    | 0 | * | * | * |  |  |

| 177   | ANA H          | A4      | 1      | 4     | A = A * H       | *    | 0 | * | * | * |  |  |

| 178   | ANA L          | A5      | 1      | 4     | A = A * L       | *    | 0 | * | * | * |  |  |

| 179   | ANA M          | A6      | 1      | 7     | A = A * M       | *    | 0 | * | * | * |  |  |

| 180   | ANA A          | A7      | 1      | 4     | A = A * A       | *    | 0 | * | * | * |  |  |

| The ( | OR Operation   |         | '      | 1     | •               | '    |   |   |   |   |  |  |

| 181   | ORI d8         | F6-d8   | 2      | 7     | $A = A \lor d8$ | *    | 0 | 0 | * | * |  |  |

| 182   | ORA B          | В0      | 1      | 4     | $A = A \lor B$  | *    | 0 | 0 | * | * |  |  |

| 183   | ORA C          | B1      | 1      | 4     | $A = A \lor C$  | *    | 0 | 0 | * | * |  |  |

| 184   | ORA D          | B2      | 1      | 4     | $A = A \lor D$  | *    | 0 | 0 | * | * |  |  |

| 185   | ORA E          | В3      | 1      | 4     | $A = A \lor E$  | *    | 0 | 0 | * | * |  |  |

| 186   | ORA H          | B4      | 1      | 4     | $A = A \lor H$  | *    | 0 | 0 | * | * |  |  |

| 187   | ORA L          | B5      | 1      | 4     | $A = A \lor L$  | *    | 0 | 0 | * | * |  |  |

| 188   | ORA M          | B6      | 1      | 7     | $A = A \lor M$  | *    | 0 | 0 | * | * |  |  |

| 189   | ORA A          | B7      | 1      | 4     | $A = A \lor A$  | *    | 0 | 0 | * | * |  |  |

|       | Exclusive-OR ( |         | 1      | 1     | 1               | 1    | 1 | 1 |   |   |  |  |

| 190   | XRI d8         | EE-d8   | 2      | 7     | A = A XOR d8    | *    | 0 | 0 | * | * |  |  |

| 191   | XRA B          | A8      | 1      | 4     | A = A XOR B     | *    | 0 | 0 | * | * |  |  |

| 192   | XRA C          | A9      | 1      | 4     | A = A XOR C     | *    | 0 | 0 | * | * |  |  |

| 193   | XRA D          | AA      | 1      | 4     | A = A XOR D     | *    | 0 | 0 | * | * |  |  |

| 194   | XRA E          | AB      | 1      | 4     | A = A XOR E     | *    | 0 | 0 | * | * |  |  |

| SL    | Mnemonic        | On anda      | Op-code Bytes | Clock | Function                        |     | Flag |   |   |   |  |  |

|-------|-----------------|--------------|---------------|-------|---------------------------------|-----|------|---|---|---|--|--|

| SL    | Millemonic      | Op-code      | Dytes         | Clock | Function                        | Z   | C    | A | S | P |  |  |

| 195   | XRA H           | AC           | 1             | 4     | A = A XOR H                     | *   | 0    | 0 | * | * |  |  |

| 196   | XRA L           | AD           | 1             | 4     | A = A XOR L                     | *   | 0    | 0 | * | * |  |  |

| 197   | XRA M           | AE           | 1             | 7     | A = A XOR M                     | *   | 0    | 0 | * | * |  |  |

| 198   | XRA A           | AF           | 1             | 4     | A = A XOR A                     | 1   | 0    | 0 | 0 | 1 |  |  |

| Rotat | e Instructions  |              |               |       |                                 |     |      |   |   |   |  |  |

| 199   | RLC             | 07           | 1             | 4     | Rotate A left                   | -   | *    | - | - | - |  |  |

| 200   | RRC             | 0F           | 1             | 4     | Rotate A right                  | -   | *    | - | - | - |  |  |

| 201   | RAL             | 17           | 1             | 4     | Rotate A left thru Cary         | -   | *    | - | - | - |  |  |

| 202   | RAR             | 1F           | 1             | 4     | Rotate A right thru Carry       | -   | *    | - | - | - |  |  |

| Progr | ram Control In  | structions   |               |       |                                 |     |      |   |   |   |  |  |

| Uncor | nditional Jump  | Instructions |               |       |                                 |     |      |   |   |   |  |  |

| 203   | JMP a16         | C3-ll-hh     | 3             | 10    | Program continues at a16        | -   | -    | - | - | - |  |  |

| 204   | PCHL            | E9           | 1             | 6     | Program continues at address HL | -   | -    | - | - | - |  |  |

| Cond  | itional Jump II | nstructions  | •             | •     |                                 |     |      |   |   |   |  |  |

| 205   | JZ a16          | CA-ll-hh     | 3             | 7/10  | Jump if zero                    | -   | -    | - | - | - |  |  |

| 206   | JNZ a16         | C2-ll-hh     | 3             | 7/10  | Jump if not zero                | -   | -    | - | - | - |  |  |

| 207   | JC a16          | DA-ll-hh     | 3             | 7/10  | Jump if carry set               | -   | -    | - | - | - |  |  |

| 208   | JNC a16         | D2-ll-hh     | 3             | 7/10  | Jump if carry cleared           | l - | _    | - | - | - |  |  |

| 209   | JM a16          | FA-ll-hh     | 3             | 7/10  | Jump if minus                   | -   | _    | - | _ | - |  |  |

| 210   | JP a16          | F2-ll-hh     | 3             | 7/10  | Jump if positive                | -   | _    | - | _ | - |  |  |

| 211   | JPE a16         | EA-ll-hh     | 3             | 7/10  | Jump if parity even             | -   | _    | - | _ | - |  |  |

| 212   | JPO a16         | E2-ll-hh     | 3             | 7/10  | Jump if parity odd              | -   | _    | - | _ | - |  |  |

|       | ng to a Subrou  |              |               | ,,,,, | t same of parties               |     |      |   |   |   |  |  |

| 213   | CALL a16        | CE-ll-hh     | 3             | 18    | Call subroutine at a16          | -   | _    | _ | _ | - |  |  |

| 214   | CC a16          | DC-ll-hh     | 3             | 9/18  | Call subroutine on carry        | -   | _    | - | - | - |  |  |

| 215   | CNC a16         | D4-ll-hh     | 3             | 9/18  | Call subroutine on no carry     | -   | _    | _ | - | - |  |  |

| 216   | CZ a16          | CC-ll-hh     | 3             | 9/18  | Call subroutine on zero         | -   | -    | - | - | - |  |  |

| 217   | CNZ a16         | C4-ll-hh     | 3             | 9/18  | Call subroutine on not zero     | ļ - | _    | _ | - | - |  |  |

| 218   | CM a16          | FC-ll-hh     | 3             | 9/18  | Call subroutine on minus        | ļ - | -    | - | - | - |  |  |

| 219   | CP a16          | F4-ll-hh     | 3             | 9/18  | Call subroutine on positive     | ļ - | _    | - | _ | - |  |  |

| 220   | CPE a16         | EC-ll-hh     | 3             | 9/18  | Call sub on parity even         | -   | -    | - | - | - |  |  |

| 221   | CPO a16         | E4-ll-hh     | 3             | 9/18  | Call sub on parity odd          | l - | _    | - | _ | _ |  |  |

|       | rning from a su |              |               |       | ,                               |     | !    |   |   |   |  |  |

| 222   | RET             | C9           | 1             | 10    | Return from subroutine          | -   | _    | - | _ | _ |  |  |

| 223   | RC              | D8           | 1             | 6/12  | Return if carry set             | -   | _    | - | - | _ |  |  |

| 224   | RNC             | D0           | 1             | 6/12  | Return if carry cleared         | -   | _    | - | - | _ |  |  |

| 225   | RZ              | C8           | 1             | 6/12  | Return if zero                  | -   | _    | _ | - | _ |  |  |

| 226   | RNZ             | C0           | 1             | 6/12  | Return if not zero              | -   | _    | _ | - | _ |  |  |

| 227   | RM              | F8           | 1             | 6/12  | Return if minus                 | -   | -    | - | - | - |  |  |

| 228   | RP              | F0           | 1             | 6/12  | Return if positive              | -   | -    | - | - | - |  |  |

| 229   | RPE             | E8           | 1             | 6/12  | Return if parity even           | -   | -    | - | - | - |  |  |

| 230   | RPO             | E0           | 1             | 6/12  | Return if parity odd            | ļ - | -    | - | - | - |  |  |

|       | rt Instructions |              | _             |       |                                 |     |      |   |   |   |  |  |

|       | RST 0           | C7           | 1             | 12    | Call subroutine at 0000H        | -   | -    | _ | _ | _ |  |  |

| 231   |                 |              |               |       |                                 | 1   | 1    | 1 | 1 | 1 |  |  |

| 231   | RST 1           | CF           | 1             | 12    | Call subroutine at 0008H        | -   | _    | - | _ | _ |  |  |

Prof. (Dr.) Saibal Pradhan, CEMK

| SL    | Mnemonic         | Op-code          | Bytes | Clock | Function                      | Flag |   |   |   |   |

|-------|------------------|------------------|-------|-------|-------------------------------|------|---|---|---|---|

|       |                  |                  |       |       |                               | Z    | C | A | S | P |

| 234   | RST 3            | DF               | 1     | 12    | Call subroutine at 0018H      | -    | - | - | - | - |

| 235   | RST 4            | E7               | 1     | 12    | Call subroutine at 0020H      | -    | - | - | - | - |

| 236   | RST 5            | EF               | 1     | 12    | Call subroutine at 0028H      | -    | - | - | - | - |

| 237   | RST 6            | F7               | 1     | 12    | Call subroutine at 0030H      | -    | - | - | - | - |

| 238   | RST 7            | FF               | 1     | 12    | Call subroutine at 0038H      | -    | - | - | - | - |

| Misco | ellaneous Instri | uctions          | •     | •     |                               |      |   |   |   |   |

| Micro | oprocessor Con   | trol Instruction | ons   |       |                               |      |   |   |   |   |

| 239   | NOP              | 00               | 1     | 4     | Performs no operation         | -    | - | - | - | - |

| 240   | STC              | 37               | 1     | 4     | Set carry flag                | -    | 1 | - | - | - |

| 241   | CMC              | 3F               | 1     | 4     | Complement carry flag         | -    | * | - | - | - |

| 242   | HLT              | 76               | 1     | 4     | Halt until reset or interrupt | -    | - | - | - | - |

| 243   | EI               | FB               | 1     | 4     | Enable interrupts             | -    | - | - | - | - |

| 244   | DI               | F3               | 1     | 4     | Disable interrupts            | -    | - | - | - | - |

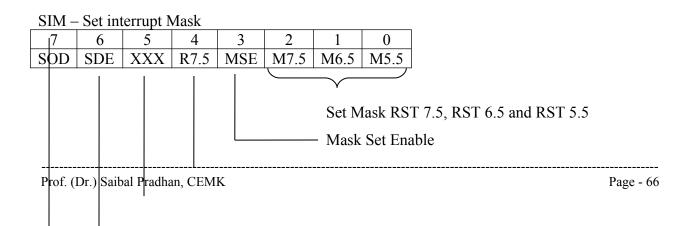

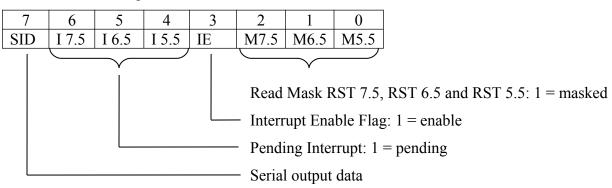

| 245   | RIM              | 20               | 1     | 4     | Read interrupt mask           | -    | - | - | - | - |

| 246   | SIM              | 30               | 1     | 4     | Set interrupt mask            | -    | - | - | - | - |

| Note  | : -, no change;  | *, changes;      |       |       |                               |      |   |   |   |   |

#### **Sample Questions and Solutions:**

- 1. Write a sequence of immediate instructions that will place a 0000 in BC and a 12H in Accumulator?

- 2. Write a sequence of immediate instructions that will store 16H in memory location 1200H and a 17H in memory location 1202H?

- 3. Explain how does the LDA 1000H instruction function?

- 4. Explain what answer is found in memory locations 1200H and 1201H after the execution of the following instructions

MVI H, 22H MVI L, 44H SHLD 1200H

5. Explain what answer is found in memory locations 1200H in the following sequence of instructions.

MVI B, 12H MVI C, 00H MVI A, 77H STAX B

- 6. Write a sequence of instructions that will use register indirect addressing to transfer the number stored in memory location 1300H into memory location 1301H.

- 7. Explain what does the MOV M, C instruction do if HL=1234H and C=34H.

- 8. Write a sequence of instructions that use MOV instructions to swap the contents of the BC to DE register pairs.

- 9. Write a sequence of instructions that will store a zero in memory location 1000H through 10003H.

- 10. If a 1000H is pushed into the stack followed by a 2000H, which number is the first to come off the stack?

- 11. What number appears in BC register pair after the following sequence of instructions.

LXI H, 3000H LXI D, 2500H PUSH H PUSH D POP H POP B

- 12. If a PUSH PSW is immediately followed by a POP B, in which register do the flag data appear?

- 13. Write a sequence of instructions that will add a 56H to the number in the B register.

- 14. Write a sequence of instructions that will add the content of H to that of L register.

- 15. Write a sequence of instructions that will add the content of HL to that of DE register pair (not using DAD D)

- 16. Write a sequence of instructions that will add the BCD numbers placed in B and L registers.

- 17. Write e sequence of instructions that will one's complement the contents of DE register pair.

#### **Solutions:**

1. Write a sequence of immediate instructions that will place a 0000 in BC and a 12H in Accumulator?

LXI B, 0000H MVI B, 00H or MVI C, 00H MVI A, 12H MVI A, 12H

2. Write a sequence of immediate instructions that will store 16H in memory location 1200H and a 17H in memory location 1202H?

LXI H, 1200H MVI M, 16H INX H INX H MVI M, 17H

3. Explain how does the LDA 1000H instruction function?

After the execution of the instruction, the content of memory having address 1000H is loaded into accumulator.

4. Explain what answer is found in memory locations 1200H and 1201H after the execution of the following instructions

MVI H, 22H MVI L, 44H SHLD 1200H

After the execution of the first two instructions, the content of HL register pair will be 2214H. SHLD instruction is a direct mode of instruction after execution of which the content of L and H registers will be stored in memory location1200H and 1201H respectively.

5. Explain what answer is found in memory locations 1200H in the following sequence of instructions.

MVI B, 12H MVI C, 00H MVI A, 77H STAX B

After the execution of first two instructions, BC register pair will initialized with 1200H. The third instruction stores 77H in accumulator. The final instruction is a register indirect mode of instruction which stores the content of accumulator in memory location pointed out by BC register pair. Therefore, the accumulator value (77H) will be stored in memory location 1200H.

6. Write a sequence of instructions that will use register indirect addressing to transfer the number stored in memory location 1300H into memory location 1301H.

Prof. (Dr.) Saibal Pradhan, CEMK

LXI B, 1300H LDAX B INX B STAX B

7. Explain what does the MOV M, C instruction do if HL=1234H and C=34H.

The instruction MOV M, C stores the content of register C in memory location pointed out by HL register pair. In the present case, C=34H and HL=1234H, thus the data 34H will be stored in memory location 1234H.

8. Write a sequence of instructions that use MOV instructions to swap the contents of the BC to DE register pairs.

MOV H, B ; content of BC is temporarily stored in HL

MOV L, C

MOV B, D; content of DE is stored in BC

MOV C, E

MOV D, H ; finally the content of BC kept aside in HL is stored in DE

MOV E, L

9. Write a sequence of instructions that will store a zero in memory location 1000H through 10003H.

LXI H, 1000H ; HL = 1000H

MOV A, L MOV M, A

INX H ; HL =1001H

MOV M, A

INX H ; HL = 1002H

MOV M, A

INX H

MOV M, A ; HL = 1003H

HLT

This is an example of iteration i.e. repetitive work. The above piece of program stores values in four memory locations by using four separate instructions which is not efficient in case of large number of iteration. Large iterations are implemented by repeating a group of instructions in a number of times called looping and is demonstrated below with the same example. A counter is used to control looping:

LXI H, 1000H ; memory pointer

MVI C, 04H ; four memory locations to be loaded

LOOP: MOV M, A ; data stored in memory

INX H ; pointer updated for next memory

DCR C ; counter decremented

JNZ LOOP; the process is repeated until counter is zero

HLT

10. If a 1000H is pushed into the stack followed by a 2000H, which number is the first to come off the stack?

In the present case, 1000H is PUSHed first and then 2000H. As stack is a LIFO memory, the last data PUSHed (2000H) in stack will be retrieved first.

11. What number appears in BC register pair after the following sequence of instructions.

LXI H, 3000H LXI D, 2500H PUSH H PUSH D POP H POP B

Content of HL is pushed in stack first and then the content of DE. Poping of HL is done first and then BC. Therefore, POP H stores the value of DE (as pushed last) in HL (2500H) while POP B retrieves the original value of HL in BC which is 3000H.

12. If a PUSH PSW is immediately followed by a POP B, in which register do the flag data appear?

PSW, the program status word, is the combination of Accumulator (msb) and flag register (lsb). Thus execution of POP B immediately after PUSH PSW will retrieve the value of Accumulator plus flag register in BC register pair. The value of accumulator will appear in B and that of flag register in C.

13. Write a sequence of instructions that will add a 56H to the number in the B register.

MVI A, 56H ADD B

14. Write a sequence of instructions that will add the content of H to that of L register.

MOV A, H ADD L

15. Write a sequence of instructions that will add the content of HL to that of DE register pair (not using DAD D)

MOV A, E ADD L

MOV L, A ; low byte of result is placed in L

MOV A, D ADC H

MOV H, A ; high byte result is placed in H and carry, if any, is available in CY flag

16. Write a sequence of instructions that will add the BCD numbers placed in B and L registers.

MOV A, B ADD L

DAA ; result is in Accumulator and carry, if any, is available in CY flag.

17. Write a sequence of instructions that will do one's complement to the contents of DE register pair.

MOV A, E

CMA

MOV E, A

MOV A, D

CMA

MOV D, A

## **Assembly Language Programming**

Lecture-10

#### **Assembly Language Programming:**

- The sequence of commands used to tell a microprocessor what to do is called a program. The commands are called instructions.

- Some part of it is called Monitor Program or Operating System and the other is called User Program or Application Program

- Operating Program basically organizes the inputs and the outputs with the system

- User Program supplies the variables and their formats

- Microprocessor can only understand the instructions coded in binary called machine language.

- Machine language is difficult, if not impossible, for human to handle.

- Assembly language was developed to provide *mnemonics* plus other features to make the programming easy, faster and less prone to error.

- Instructions abbreviated in English letters to represent the operation to be performed by the microprocessor are called *mnemonics*.

- Assembly language programs must be translated into machine code by a program called assembler.

- Assembly language is referred to as a low-level language because it deals directly with the internal structure of the microprocessor.

- High level language like C, BASIC, Java etc. can also be used for programming.

- High level language is converted into machine code by a program called *compiler*.

#### **Structure of Assembly Language:**

- An assembly language program consists of a number of assembly language instructions used to tell the CPU what to do.

- It also contains instructions giving direction to the assembler called *directives*.

- For example, MOV, ADA instructions are commands to the CPU whereas ORG, END are directives to the assembler. ORG followed by an address tells the assembler to place the op-code at that memory location while END indicates the end of the source code.

- An assembly language instruction consists of five fields:

[label:] mnemonic [destination operand] [source operand] [;comment]

- Brackets indicate that a field is optional and not all lines have them. Brackets should not be typed in.

- The label field allows the program to refer to a line of code by name. There are rules for writing the label like type & maximum number of characters, starting characters etc. which is assembler specific.

- The assembly language mnemonic together with the operands forms the command for the CPU. For example MOV A, B. MOV is the mnemonic, which is the abbreviation of data movement. The operands are supplied by A and B registers. The data from source register B moves to destination register A.

- The comment field begins with a semicolon. Comments may be at the end of a line or on a line itself. The assembler ignores comments, but they should be present to make the program understandable to others and at a later time.

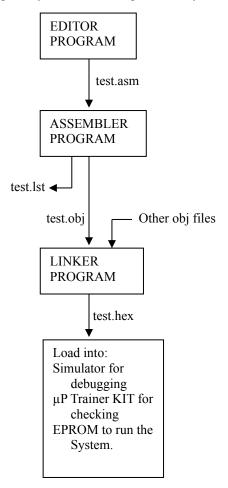

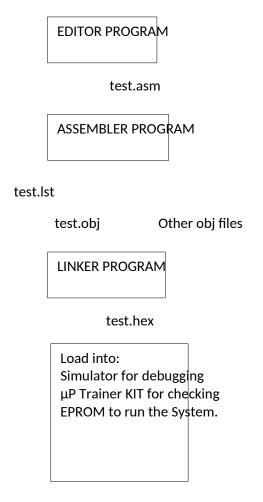

#### Assembling and running of an 8085A program:

- A machine can only understand machine language. So assembly language program is to be translated back into machine language. Human for convenience uses assembly language.

- Assembly language program is time consuming and difficult, if not impossible, to translate into machine language manually.

- A PC based program called an assembler can do the same instantaneously. It takes an assembly language program as input, and produces an object file having extension .obj for machine codes.

- The assembly language file can be written in any EDITOR program like DOS EDIT, WINDOWS NOTEPAD etc. which saves the file in ASCII format having extension .asm.

\_\_\_\_\_\_

- Program can also be written in high level languages like 'C', BASIC, PASCAL. An interpreter program or a compiler is used to translate the same into machine codes.

- All the object files created by assembler or compiler can then be combined together to form a single machine language program by another program called linker.

- The total flow diagram of machine language program development is depicted below.